OP AMP 포스팅 입니다. 본 포스팅은위키를 참고하여 작성했습니다.

우리가 흔히 아는 OP AMP는 아래와 같이 생겨먹었다.

이 증폭기의 기본 정의 중 중요한거 세가지를 꼽으라면 아래와 같을 것이다.

- 입력 임피던스는 무한

- 출력 임피던스는 0

- 개방 이득 A는 무한

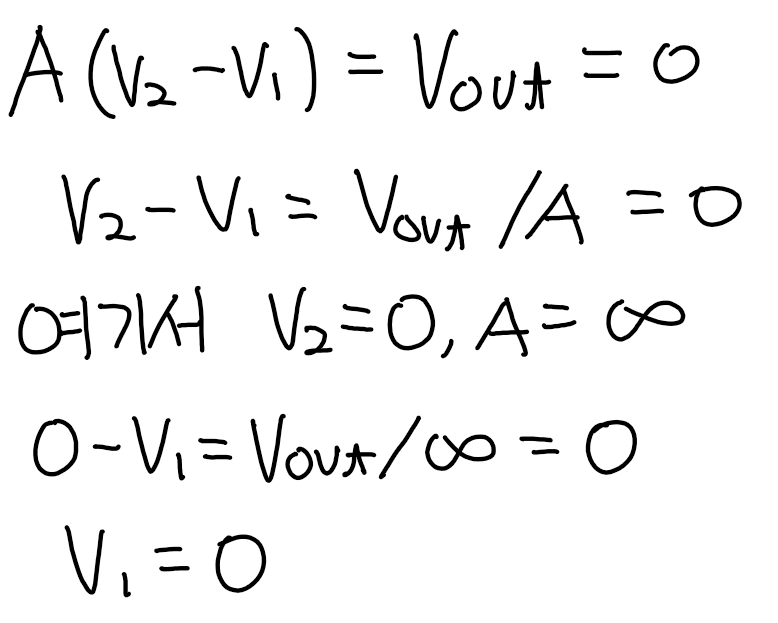

이번에는 3번을 중심으로 짚어보고자 한다.

보통 이런식으로 Feedback을 구성하지 않는 경우를 비교기로 활용한다.

V+가 크면 플러스 무한대로, V-가 더 크면 마이너스 무한대로 갈 것이다.

하지만 실제 전원공급을 Vs+ Vs-로 공급을 한다면, V+가 클경우 Vs+, V-가 더 크면 Vs-가 출력될 것이다. 출력 전압은 공급 전원을 초과할 수 없을 것이다.

반전증폭기

그런데 위의 경우는 개방이득이 무한대이므로, 2배만 증폭하거나 10배를 증폭하는 용도로 사용할 수 없다. 그래서 피드백을 구성해서 회로를 만든다.

위 회로를 보자. 이렇게 회로를 구성한다고 해봤자 개방이득이 무한대인건 똑같다. 하지만 실험을 해보면 출력 전압은 개방 이득의 영향을 받지 않는다. 이 말인 즉 수식이 아래와 같다는거다.

따라서 V1은 0V이며, 이를 Virtual Ground(가상 접지)라고 부르기도 한다.

위의 Vout은 개방 루프 관점에서 봐서 그런것이고, 루프 회로일 때를 따로 따져봐야한다.

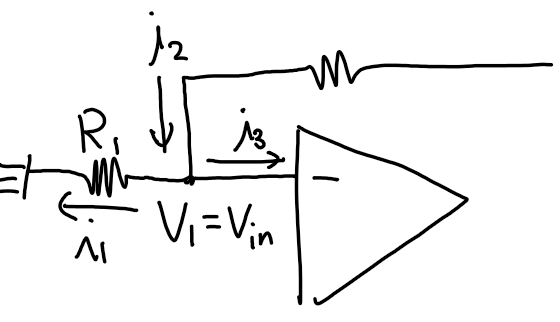

V1에서 OpAmp로 흘러가는 전류는 없을 것이다. 왜냐면 입력 임피던스가 무한대이므로, 연산 증폭기 내부로 전류가 흘러갈 수는 없기 때문이다.

그렇다면 V1을 기준으로 회로를 그려보자면 아래와 같을 것이다.

이전에 언급한 것과 같이 i3는 입력임피던스가 무한이므로 0이다. 따라서 i1과 i2를 V=I x R 공식에 따라 수식을 전개하고 정리하면 출력 전압을 구할 수 있다.

위에 정리해 둔 것과 같이 출력 전압은 입력 신호의 반전 형태이므로 반전 증폭기라 부른다.

비반전증폭기

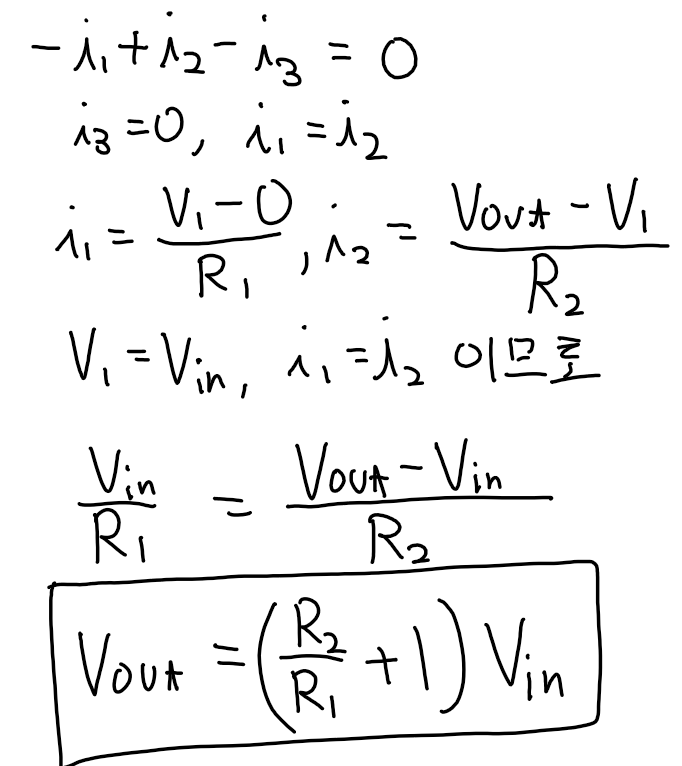

비 반전 증폭기도 크게 다르지 않다. V1=V2인 것이 이전 반전 증폭기 파트에서 나타났으므로 이를 적극 활용한다.

입력 Vin을 반전 단자에서 비반전 단자에서 바뀐것을 빼곤 회로는 똑같다.

V1부분을 확대해서 회로를 보면 아래와 같을 것이다.

i3는 입력 임피던스가 무한이므로 0일 것이고 이를 이용하여 수식을 전개하면 아래와 같을 것이다.

최종적으로 정리된 값을 보면 출력 전압은 입력 파형과 같은 동상이므로, 비반전 증폭기라 부른다. 특이점이라면 무조건 1보다 큰 값을 가지므로, 증폭을 하지 않고 필터만 하고 싶다면 반전 증폭기를 사용해야 할 것이다.

정리

반전은 증폭을 하지 않고 필터 처리만 하는 것도 가능하지만, 비반전은 무조건 증폭이 된다.

끗.

OPamp로 저의 시간도 증폭해주실 수 있나요? 그럼 퇴근시간이 될거 같은데 ㅎㅎ 푸하핳